Legacy Downtime costs $9,000/min. Are you protected?

Get a Free AssessmentUncover the future of SPARC Emulation with Charon SSP.

Download Datasheet

Explain: What is the SPARC architecture, its history, and key features?

Explain: What is the SPARC architecture, its history, and key features?SPARC (Scalable Processor Architecture) was introduced by Sun Microsystems in 1987. It is still powering NASA’s 2020 Solar Orbiter mission and is an open, non-proprietary, and royalty-free 32/64-bit architecture. It features register windows for efficient context switching, load/store operations, and scalability from embedded systems to servers. It is widely used in UNIX-based systems, such as the Solaris operating system, for critical operations.

SPARC hardware was popular for its high performance, flexibility, and ease of development. Despite competition and aging hardware challenges, SPARC remains vital for mission-critical applications, such as Oracle Solaris workloads. Modern virtualization and emulation solutions, such as Stromasys Charon, enable organizations to preserve existing Solaris workloads while migrating to contemporary platforms, ensuring business continuity and mitigating risks associated with legacy SPARC hardware.

Articles

ArticlesDid you know that the NASA/ESA Solar Orbiter mission launched in 2020 is powered by technology from the 1990s? Yes, that’s right! It was driven by the SPARC architecture.

SPARC, a hardware architecture designed for microprocessors, was at its peak in the 1990s. While it may be decades old, some businesses are still using it.

SPARC is a widely used architecture for UNIX-based operating systems, particularly Solaris from Sun Microsystems.

In this article, we’re going to take a deeper look at the:

So, come along and explore the legacy architecture together and see what the future holds for it.

SPARC, or Scalable Processor Architecture, was introduced by Sun Microsystems in 1987, which is why many refer to it as Sun SPARC.

After launch, Sun SPARC became a popular architecture for hardware compatible with UNIX-based operating systems like Solaris. This combination is commonly used in enterprises handling business-critical Solaris applications.

SPARC is a 32-and 64-bit microprocessor architecture created as a RISC (Reduced Instruction Set Computing) type computer architecture. This means that SPARC, with RISC, uses a simple set of instructions to execute the tasks quickly. It differs from CISC (Complex Instruction Set Computing) architectures, which use a more complex set of instructions.

Here is the best way to run your SPARC systems flawlessly in the modern environments.

Another key feature is that SPARC architecture is non-proprietary. It’s often called open architecture because manufacturers can easily license it to start developing their own microprocessors and semiconductors.

Moreover, SPARC architecture allows for flexible scaling. It significantly reduces interference and context switching times. The SPARC “register window” structures allow for a significant reduction in in-memory load/store guidelines sets.

| Objective | Description |

|---|---|

| Compiler & Pipeline Optimization | Designed for efficient compiler targeting and pipelined hardware |

| RISC Simplicity | Simple instruction set for speed and ease of implementation |

| Scalability | Supports a wide range of systems, from embedded to servers |

| Open Architecture | Non-proprietary, licensable by any manufacturer |

| Efficient Register Usage | Register windows for fast context switching and reduced memory access |

| Minimal Microcode | Most operations in hardware for higher speed |

| High Execution Rates & Fast Development | Focus on high MIPS and rapid product development |

| Efficient Argument Passing & Branching | Registers and delay slots for optimized function calls and branches |

Firstly, the word “Scalable” in SPARC means it can be used for anything from small embedded systems to powerful server processors. This scalability meant that as circuit technology improved, the cost-to-performance ratio of new SPARC implementations would also improve.

Secondly, the main goal of developing the Sun SPARC architecture was to enhance compilers’ efficiency and seamlessly pipelined hardware implementations. The SPARC implementation also aims at higher execution rates, which translate into faster processing speeds.

Finally, SPARC’s design allowed for quicker development cycles, meaning products could hit the market faster.

Generally, we can categorize the history of SPARC into three phases:

SPARC’s journey began in 1984. The initial development phase culminated in 1986 with the introduction of Sun’s first SPARC processor, SPARC V7. The next year, the first SPARC workstation was launched.

As the architecture evolved, SPARC International was established in 1989 with the instruction set architecture (ISA).

In 2010, Oracle Corporation acquired Sun Microsystems, which brought fresh resources and a new direction to SPARC development.

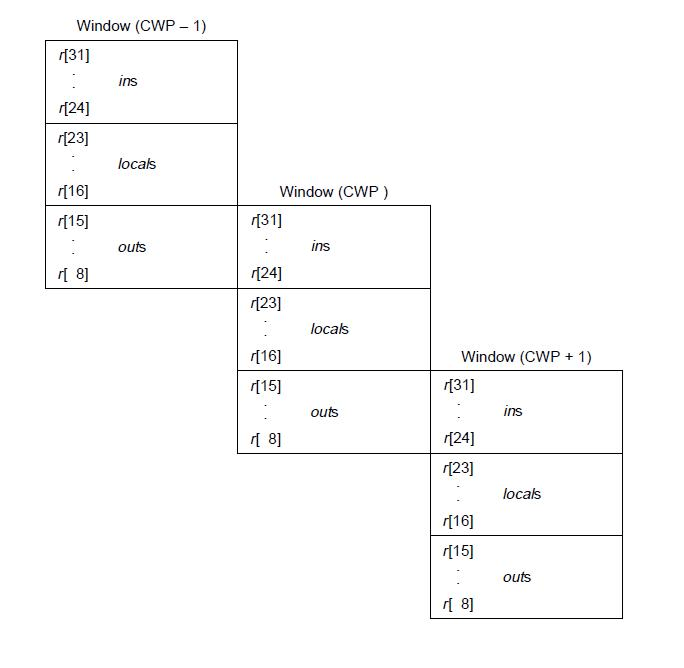

First and foremost, SPARC is a load and store architecture, meaning operations are executed over registers. This is why it uses a register window concept to offer many registers.

Additionally, a delay slot is used to optimize branch instructions. Using these registers and the stack allows arguments to be passed efficiently.

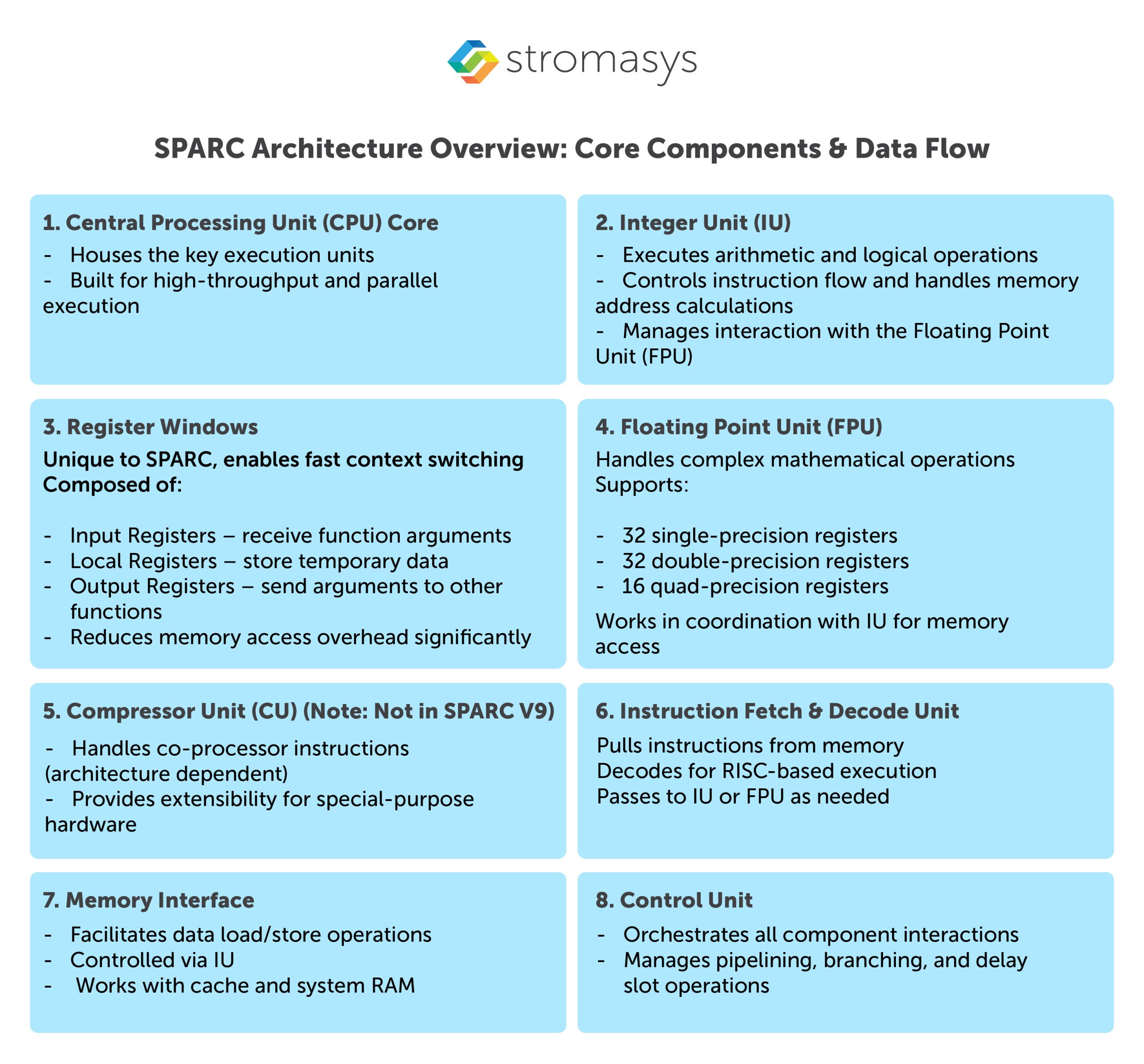

The key modules of the SPARC architecture are as follows:

The Integer Unit (IU) in the SPARC architecture is central to the processor’s operation. It contains many general-purpose registers, ranging from 64 to 528. These are divided into:

The IU executes all integer arithmetic instructions and calculates memory addresses for load and store operations. It also manages the program counters and controls the instruction execution for the Floating Point Unit (FPU).

In the SPARC architecture, an instruction can access the eight global registers and a 24-register window at any time.

A register window consists of a 16-register set, which is divided into:

Additionally, it also includes the eight in registers of an adjacent register set, which are addressable from the current window as its out registers.

When a procedure is called, the register window shifts by sixteen registers. This shift hides the old input and local registers, and the old output registers become the new input registers.

Here’s how the registers are used:

The Floating-Point Unit (FPU) in the SPARC architecture is designed to handle floating-point operations efficiently. It has:

Double-precision values use an even-odd pair of single-precision registers, while quad-precision values use an odd-even pair of double-precision registers.

To move data between the FPU and memory, floating-point load/store instructions are used. The memory address for these operations is calculated by the Integer Unit (IU).

Floating-Point operate (FPop) instructions perform floating-point arithmetic operations and comparisons.

The SPARC architecture’s Compressor Unit (CU) includes support for a single, implementation-dependent coprocessor, which has its own set of registers.

Coprocessor load/store instructions move data between the coprocessor registers and memory. The floating-point instructions mirror the coprocessor instructions.

Note: There is no Compressor Unit in SPARC V9.

The SPARC architecture has several distinctive features:

It uses a higher number of instruction sets and fewer transistors, making it a disentangled and efficient design.

SPARC architecture is highly flexible in terms of capacity and cost. Its integration of memory, cache, and FPUs (Floating-Point Units) is very adaptable.

It offers flexibility in licensing and allows users to configure their solutions using the SPARC architecture.

The SPARC architecture is versatile and scalable. One of the prime example is the Sun4d platform. It scaled up to 20 processors in the early 1990s, which is a proof to how seriously SPARC took enterprise-grade scalability from the very beginning. It is, therefore, suitable for various applications, including military, technology, aerospace, and many others.

It maintains compatibility across different generations of architecture that ensure longevity and ease of upgrades.

SPARC supports object-oriented programming features, enhancing its programming capabilities.

Here are some advantages of operating on SPARC platforms:

The SPARC architecture is simple and efficient. This makes it both powerful and easy to use.

SPARC is designed to meet its users’ high expectations and deliver high performance in real-world applications while keeping costs low.

SPARC systems often provide 60%-85% more efficiency per core. Thus, you get more performance out of each processor core.

Sun SPARC processors (i.e. Sun servers with SPARC processors) offer excellent flexibility and scalability, along with a high level of availability. This makes them ideal for various demanding applications.

The SPARC-V9 architecture supports multiple threads per core, which reduces CPU idle time and increases overall CPU utilization. The Sun4v extended that further by enabling multiple OS instances to share the same hardware efficiently via the hypervisor. It’s a natural progression of the same idea, which is from thread-level efficiency to system-level efficiency. This leads to better performance.

SPARC faces considerable competition from competitors such as x86, ARM, and others. x86 is known for its compatibility with various applications, whereas ARM is popular because of its energy-efficient designs.

SPARC isn’t typically used in educational settings. It’s more commonly used by developers and computer architects for server applications and low-level programming (unlike more popular educational architectures like MIPS and ARM).

Since SPARC is an open architecture, it’s accessible to everyone. This openness can lead to the risk of misuse by individuals who might use SPARC-based products improperly.

SPARC has been handling mission-critical workloads for organizations for more than 20 years now. It’s known for its excellent scalability, high-end computing, and solid security.

However, like any legacy hardware, it struggles to handle large amounts of data without significant downtime, which poses a serious business risk. According to Gartner, the average cost of downtime is $5600 per minute.

The aging SPARC hardware also has a huge maintenance cost. Reliability is also an alarming issue here. Furthermore, finding skilled professionals who can provide modern data support becomes challenging with every passing year. Again, finding replacement parts can be frustrating.

Well, let’s not forget about the opportunity cost. For instance, a legacy SPARC machine could hinder your plan to move on-premises equipment to a hybrid cloud model as it isn’t certified for use in the hybrid cloud management platform.

All these costs and operational challenges are daunting. So, is this the end of your SPARC hardware?

Sticking to outdated SPARC hardware keeps your IT team looking backward when they should be driving innovation and looking ahead.

Don’t worry. Stromasy can offer a risk-free, cost-effective and frictionless solution. With our SPARC emulator, Charon-SSP, you can easily migrate your Solaris applications to modern platforms, whether on-premises or in the cloud.

The best part? The migration process doesn’t alter your critical Solaris applications and can be completed without any disruption to your business operations. In fact, your end users will not notice any changes.

So, are you ready to eliminate the risk of business failure associated with your old SPARC hardware? The ROI of this lift and shift process is substantially high.

Would you like to know more?

Get a proven solution from our experts specifically created for your business.

SPARC (Scalable Processor Architecture) is a type of processor design created by Sun Microsystems. It’s known for handling demanding computing tasks, often found in servers and powerful workstations.

Basically, it’s a load and store design, which means that it only processes data that’s in the CPU SPARC registers. Data is fetched from memory and placed into registers before being processed and then stored back into memory after processing.

SPARC stands for Scalable Processor Architecture.

The SPARC framework is a set of guidelines for implementing and using the SPARC architecture in computing systems. It ensures that the systems are scalable, efficient, and perform well.

The Sun SPARC processor is used by organizations that need robust computing power, like data centers, big enterprises running complex applications, and research institutions that rely on heavy computational tasks.

Tuhin is a passionate writer with more than 7 years of experience in technical and marketing writing. With a unique ability to connect with his readers on a deeper level, he crafts content that not only captivates but also inspires action. Always on the cutting edge of industry trends, he excels at breaking down complex ideas into clear, engaging narratives that drive engagement and fuel business growth. Beyond his inherent inclination for writing, he is a sports enthusiast and a traveller, always seeking new experiences to enrich his perspective and creativity.

The corporate IT landscape is evolving rapidly, presenting significant challenges for businesses. One major issue...

Read MoreAre you looking to eliminate the risks associated with your HP 9000 PA-RISC systems? If...

Read MoreDid you know? HP discontinued the sales of PA-RISC systems in 2008 and ended support...

Read MoreDon't let your legacy systems slow you down! Contact us today and transform your legacy environment into a dynamic, agile platform for success.

Kickstart your journey towards a more efficient and streamlined business environment with just one click.